## Lógica secuencial

## 6-1 INTRODUCCION

Los circuitos digitales hasta ahora considerados han sido combinacionales, es decir, las salidas en un instante dado de tiempo son enteramente dependientes de las entradas presentes en ese mismo tiempo. Aunque cada sistema digital debe tener circuitos combinacionales, la mayoría de los sistemas encontrados en la práctica incluyen también elementos de memoria, los cuales requieren que el sistema se describa en términos de la lógica secuencial.

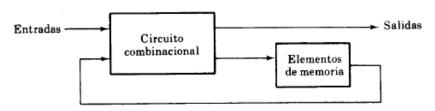

Un diagrama de bloque de un circuito secuencial se muestra en la Figura 6-1. Este consiste en un circuito combinacional al cual se le conectan elementos de memoria para formar un camino de realimentación. Los elementos de memoria son capaces de almacenar información binaria dentro de ellos. La información binaria almacenada en los elementos de memoria en un tiempo dado define el estado del circuito secuencial. El circuito secuencial recibe la información binaria de las entradas externas. Estas entradas, conjuntamente con el presente estado de los elementos de memoria, determinan el valor binario de los terminales de salida. También determinan la condición de cambio de estado en los elementos de memoria. El diagrama de bloque demuestra que las salidas externas en un circuito secuencial son una función no solamente de las entradas externas sino del presente estado de los elementos de memoria. El siguiente estado de los elementos de memoria es también una función de las entradas externas y del estado presente. Así, un circuito secuencial se especifica por medio de una secuencia de tiempo de las entradas, salidas y estados internos.

Hay dos tipos de circuitos secuenciales. Su clasificación depende del tiempo de sus señales. Un circuito secuencial sincrónico es un sistema cuyo comportamiento puede definirse a partir del conocimiento de sus señales en instantes discretos de tiempo. El comportamiento de un circuito asincrónico depende del orden en que cambien las señales de entrada y puedan ser afectadas en un instante dado de tiempo. Los elementos de memoria comúnmente usados en los circuitos secuenciales asincrónicos son mecanismos retardadores de tiempo. La capacidad de memoria de los mecanismos retardadores de tiempo se debe al hecho de que la señal

Figura 6-1 Diagrama de bloque de un circuito secuencial

gasta un tiempo finito para propagarse a través del dispositivo. En la práctica, el retardo de propagación interna de las compuertas lógicas es de una duración suficiente como para producir el retardo necesario, de tal manera que las unidades físicas de retardo de tiempo puedan ser despreciables. En los sistemas asincrónicos tipo compuerta, los elementos de memoria de la Figura 6-1 consisten en compuertas lógicas cuyos retardos de propagación constituyen la memoria requerida. Así, un circuito secuencial asincrónico puede tomarse como un circuito combinacional con realimentación. Debido a la realimentación entre las compuertas lógicas, un circuito secuencial asincrónico puede a veces volverse inestable. El problema de inestabilidad impone muchas dificultades al diseñador. Por tanto, su uso no es tan común como en los sistemas sincrónicos.

Un sistema lógico secuencial sincrónico, por definición, puede usar señales que afecten los elementos de memoria solamente en instantes de tiempo discreto. Una forma de lograr este propósito es usar pulsos de duración limitada a través del sistema de tal manera que la amplitud de un pulso represente lógica 1 y otra amplitud de pulso (o la ausencia de un pulso) represente lógica 0. La dificultad con un sistema de pulsos es que cualquier par de pulsos que lleguen de fuentes separadas independientes a las entradas de la misma compuerta mostrarán retardos no predecibles de tal manera que se separarán los pulsos ligeramente, resultando una operación no confiable.

Los sistemas lógicos secuenciales sincrónicos prácticos usan amplitudes fijas tales como niveles de voltaje para las señales binarias. La sincronización se logra por un dispositivo de tiempo llamado generador maestro de tiempo el cual genera un tren periódico de pulsos de reloj. Los pulsos de reloj se distribuyen a través del sistema de tal manera que los elementos de memoria son afectadas solamente con la llegada del pulso de sincronización. En la práctica, el pulso de reloj se aplica a las com-◆puertas AND conjuntamente con las señales que especifican los cambios requeridos en los elementos de memoria. Las salidas de la compuerta AND pueden trasmitir señales solamente en los instantes que coinciden con la llegada de los pulsos de reloj. Los circuitos secuenciales sincrónicos que usan pulsos de reloj en las entradas de los elementos de memoria se llaman circuitos secuenciales temporizados. Los circuitos secuenciales temporizados son el tipo más comúnmente usado. No presentan problemas de inestabilidad y su temporización se divide fácilmente en pasos discretos independientes, cada uno de los cuales se considera separadamente. Los circuitos secuenciales que se discuten en este libro son exclusivamente del tipo temporizado.

Los elementos de memoria usados en los circuitos secuenciales temporizados se llaman flip-flops. Estos circuitos son celdas binarias capaces de almacenar un bit de información. Un circuito flip-flop tiene dos entradas, una para el valor normal y uno para el valor complemento del bit almacenado en él. La información binaria puede entrar a un flip-flop en una variedad de formas, hecho éste, que determina diferentes tipos de flip-flops. En la siguiente sección se examinan varios tipos de flip-flops y se definen sus propiedades lógicas.

## 6-2 FLIP-FLOPS

Un circuito flip-flop puede mantener un estado binario indefinidamente (siempre y cuando se esté suministrando potencia al circuito) hasta que se cambie por una señal de entrada para cambiar estados. La principal diferencia entre varios tipos de flip-flops es el número de entradas que poseen y la manera en la cual las entradas afectan el estado binario. Los tipos de flip-flops más comunes se discuten a continuación.

## Circuito básico de un flip-flop

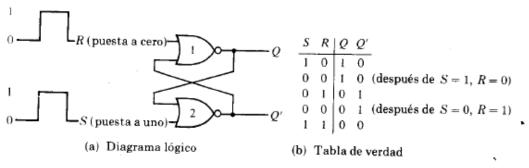

Se mencionó en las Secciones 4-7 y 4-8 que un circuito flip-flop puede construirse con dos compuertas NAND o dos compuertas NOR. Estas construcciones se muestran en los diagramas lógicos de las Figuras 6-2 y 6-3. Cada circuito forma un flip-flop básico del cual se puede construir uno más complicado. La conexión de acoplamiento intercruzado de la salida de una compuerta a la entrada de la otra constituye un camino de realimentación. Por esta razón, los circuitos se clasifican como circuitos secuenciales asincrónicos. Cada flip-flop tiene dos salidas, Q y Q' y dos entradas S (set) y R (reset). Este tipo de flip-flop se llama flip-flop RS acoplado directamente o bloqueador SR (SR latch). Las letras R y S son las iniciales de los nombres en inglés de las entradas (reset, set).

Para analizar la operación del circuito de la Figura 6-2 se debe recordar que la salida de una compuerta NOR es 0 si cualquier entrada es 1 y que la salida es 1 solamente cuando todas las entradas sean 0. Como punto de partida asúmase que la entrada de puesta a uno (set) es 1 y que la entrada de puesta a cero (reset) sea 0. Como la compuerta 2 tiene una entrada de 1, su salida Q' debe ser 0, lo cual coloca ambas entradas

Figura 6-2 Circuito flip-flop básico con compuertas NOR